助教 仙波 翔吾

## 低消費電力を目指した新しいアーキテクチャーの設計

## 概要

## ○背景

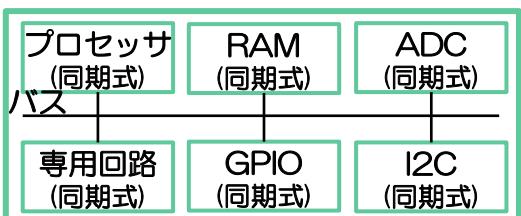

現在のデジタルシステムの多くは、System on a Chip (SoC) の概念に基づいており、クロック信号を用いた同期式回路として設計されている。しかしながら、半導体微細化技術の進歩により、クロック信号の消費電力の増加が問題となっている。

非同期式回路は、クロック信号の代わりにローカルなハンドシェイク信号を用いて各回路部品を制御する。そのため、クロック信号に関する問題を軽減することができる。しかしながら、同期式回路と比べて、非同期式回路の設計は困難である。また、SoC内の他の回路部品（例えば、マイクロプロセッサなど）が同期式回路として設計されている場合、同期式回路と非同期式回路間の接続も考慮する必要がある。

## ○目的

本研究では、同期式回路から非同期式回路への変換と、非同期式回路と同期式回路を接続するインターフェース回路の設計を支援する設計支援環境を構築し、低消費電力なデジタルシステムの実現を目指す。

## 研究概要図

## 従来のSoC

## 実用化の可能性

## ○非同期式回路による低消費電力化の実現

近年、非同期式回路の設計技術を用いた Artificial Intelligence (AI) 回路に関する研究が行われており、同期式AI回路と比べて低消費電力な非同期式AI回路が実現されている。本研究による設計支援環境を利用することによって、非同期式回路を容易にデジタルシステムに組み込むことができ、デジタルシステムの低消費電力化に寄与することが期待できる。

## UBICからのメッセージ

システム回路の高速化や高集積化と並んで、省電力化は設計における大きな課題の1つです。従来のクロック信号で制御する同期式回路の制約を外した非同期式回路は、この消費電力の問題に対する解決策の1つとなります。また近年では、AIチップへの適用に関する研究も進んでおり、これからさらなる進展も予想されます。本技術を使った新しいアーキテクチャーによる回路設計が、今後産業界にも普及していくことが期待されます。

## 非同期式回路を利用したSoC

非同期式回路として専用回路を実現することで、低消費電力化！